#### UNIVERSIDAD NACIONAL DE EDUCACIÓN A DISTANCIA

#### ESCUELA TÉCNICA SUPERIOR DE INGENIERÍA INFORMÁTICA

Proyecto de Fin de Carrera de Ingeniero Informático

# SISTEMA BASADO EN FPGA PARA LA SIMULACIÓN DINÁMICA DE CIRCUITOS ELÉCTRICOS LINEALES

VICTORINA FERNÁNDEZ GONZÁLEZ

Dirigido por: Dr. ALFONSO URQUÍA MORALEDA

Curso: 2014/2015

## SISTEMA BASADO EN FPGA PARA LA SIMULACIÓN DINÁMICA DE CIRCUITOS ELÉCTRICOS LINEALES

Proyecto de Fin de Carrera de modalidad oferta específica (tipo B)

| Realizado por: VICTORINA FERNÁNDEZ GONZÁLEZ (firma) |

|-----------------------------------------------------|

| Dirigido por: Dr. ALFONSO URQUÍA MORALERA (firma)   |

|                                                     |

|                                                     |

| Tribunal calificador:                               |

| Presidente: D./D <sup>a</sup> . (firma)             |

| Secretario: D./D <sup>a</sup>                       |

| Vocal: D./D <sup>a</sup> (firma)                    |

| Fecha de lectura y defensa:                         |

| Calificación:                                       |

| Dedicado a mi pequeña Elena, por prestarme su tiempo                                |

|-------------------------------------------------------------------------------------|

|                                                                                     |

|                                                                                     |

|                                                                                     |

| Un diseñador sabe que ha alcanzado la perfección no cuando ya no tiene nada más que |

| añadir, sino cuando ya no le queda nada más que quitar                              |

|                                                                                     |

| Antoine de Saint-Exupery                                                            |

|                                                                                     |

|                                                                                     |

|                                                                                     |

#### RESUMEN

En este proyecto fin de carrera se presenta el desarrollo de un sistema basado en FPGA para obtener simulaciones transitorias de circuitos eléctricos RLC. La arquitectura del sistema describe con VHDL tanto el método numérico para calcular los resultados de la simulación como el controlador Ethernet para intercambiar información con un PC. El método numérico elegido es el algoritmo de Runge-Kutta de cuarto orden, caracterizado por efectuar los cálculos con una precisión muy alta pero con la desventaja de requerir un gran número de operaciones.

Para el desarrollo de la arquitectura se sigue una metodología de diseño hardware con los procesos de especificación de requisitos, diseño, realización física, verificación y validación. Con la herramienta de desarrollo ISE de Xilinx se editan y analizan las descripciones VHDL, se verifican lanzando testbenches con el simulador ISim, se sintetiza y se implementa el diseño y se carga la configuración sobre una FPGA XC6SLX45 de Xilinx impresa en una tarjeta Atlys de Digilent.

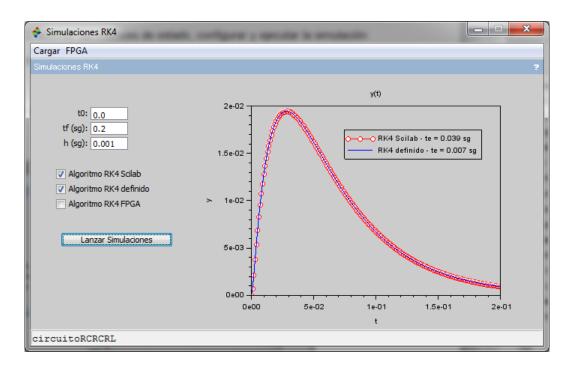

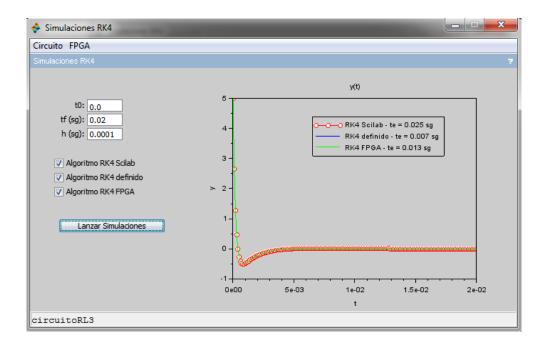

En paralelo se diseña con la herramienta de modelado, procesado y simulación Scilab una aplicación de usuario que incluye una interfaz gráfica. Con esta aplicación se genera, empleando el Análisis Nodal Modificado, el modelo de estado del circuito a partir del esquema gráfico trazado con el editor Xcos. Después se pueden ejecutar simulaciones del modelo basadas en PC o bien activar simulaciones basadas en FPGA enviando por red Ethernet el modelo del circuito a la FPGA, que procesa el algoritmo de simulación y devuelve los resultados al PC. Por último, la interfaz gráfica representa los resultados de las diferentes simulaciones junto con los tiempos de procesado empleados.

La simulación dinámica obtenida a partir de la FPGA se valida comparándola con las basadas en PC. El cálculo de los tiempos de procesado de la simulación con ambos métodos demuestra la mejora de la eficiencia cuando se emplea el sistema basado en FPGA pero teniendo en cuenta que su uso está limitado a circuitos de orden menor o igual a 16.

## **PALABRAS CLAVE**

| FPGA                            |

|---------------------------------|

| VHDL                            |

| Simulación de sistemas lineales |

| Ecuaciones diferenciales        |

| Matrices de estado              |

| Circuitos RLC                   |

| Runge-Kutta                     |

| Scilab                          |

| Xcos                            |

| Xilinx                          |

#### SUMMARY

Title: A FPGA-based system for the dynamic simulation of linear electric circuits

This final year project presents the development of a FPGA-based system for transient simulations of RLC circuits. The system architecture describes with VHDL the numerical method to solve the simulation and the Ethernet driver to exchange data with a PC. The numerical method selected is the algorithm of 4<sup>th</sup>-order Runge-Kutta, characterized by very high precision, but with the disadvantage of requiring a large number of operations.

For the development of the architecture a hardware design methodology is followed with processes as requirements specification, design, implementation, verification and validation. Using the Xilinx ISE development tool, the VHDL descriptions are edited, analyzed and verified by launching testbenches with the ISim simulator, the design is synthesized and implemented and the configuration is loaded on the Xilinx XC6SLX45 FPGA in a Digilent Atlys board.

Simultaneously, a graphical user interface is designed with the modeling, processing and simulation tool Scilab. With this application, it is generated, by means of the Modified Nodal Analysis, the state-space of the circuit from its scheme traced with Xcos. Afterwards it's possible to run PC-based simulations or activate FPGA-based simulations sending through Ethernet network the model of the circuit to the FPGA, device that processes the algorithm simulation and returns the results to the PC. Finally, the graphics representation of the solution with the simulation processing times is displayed by the user interface.

The dynamic simulation obtained by the FPGA is validated comparing with the calculated simulation by Scilab. The simulation processing times show the improvement in efficiency when using the FPGA-based system in front of the PC-based system but taking into account that its use is limited to circuits with the order less than or equal to 16.

## **KEYWORDS**

| FPGA                         |

|------------------------------|

| VHDL                         |

| Simulation of linear systems |

| Differential equations       |

| State-space matrices         |

| RLC circuits                 |

| Runge-Kutta                  |

| Scilab                       |

| Xcos                         |

| Xilinx                       |

## **ÍNDICE DE CONTENIDOS**

| IN | DICE       | DE FIGURAS                                    | 15 |

|----|------------|-----------------------------------------------|----|

| IN | DICE       | DE TABLAS                                     | 19 |

| 1. | INT        | RODUCCIÓN, OBJETIVOS Y ESTRUCTURA             | 21 |

|    | 1.1.       | Introducción                                  | 21 |

|    | 1.2.       | Objetivos                                     | 25 |

|    | 1.3.       | Estructura                                    | 26 |

| 2. | MET        | TODOLOGÍA Y HERRAMIENTAS                      | 29 |

|    | 2.1.       | Introducción                                  | 29 |

|    | 2.2.       | Metodología                                   | 29 |

|    | 2.3.       | Herramientas                                  | 30 |

|    | 2.4.       | Conclusiones                                  | 31 |

| 3. | ESP        | PECIFICACIÓN DE REQUISITOS                    | 33 |

|    | 3.1.       | Introducción                                  | 33 |

|    | 3.2.       | Funcionalidad general de la arquitectura      | 33 |

|    | 3.3.       | Flujo de datos de entrada y salida de la FPGA | 34 |

|    | 3.4.       | Algoritmo de resolución numérica              | 36 |

|    | 3.5.       | Tamaño del problema                           | 39 |

|    | 3.6.       | Representación de los datos                   | 40 |

|    | 3.7.       | Controlador de comunicación Ethernet          | 40 |

|    | 3.8.       | Almacenado de datos de entrada y salida       | 41 |

|    | 3.9.       | Activación del procesado de la simulación     | 42 |

|    | 3.10.      | Señales de reloj y reseteado                  | 42 |

|    | 3.11.      | Puertos de entrada y salida                   | 42 |

|    | 3.12.      | Conclusiones                                  | 43 |

| 4. | DIS        | EÑO CONCEPTUAL                                | 45 |

|    | <b>4</b> 1 | Introducción                                  | 45 |

| 2  | 1.2.  | Arquitectura del sistema                        | 45  |

|----|-------|-------------------------------------------------|-----|

| 2  | 1.3.  | Controlador Ethernet                            | 46  |

| 2  | 1.4.  | Memorias                                        | 49  |

| 2  | 1.5.  | Algoritmo RK4                                   | 50  |

| 4  | l.6.  | Conclusiones                                    | 54  |

| 5. | DIS   | EÑO DETALLADO                                   | 55  |

| 5  | 5.1.  | Introducción                                    | 55  |

| 5  | 5.2.  | Descripciones VHDL                              | 55  |

| 5  | 5.3.  | Memorias                                        | 75  |

| 5  | 5.4.  | Cores                                           | 79  |

| 5  | 5.5.  | Relojes                                         | 83  |

| 5  | 5.6.  | Conclusiones                                    | 88  |

| 6. | REA   | ALIZACIÓN FÍSICA                                | 89  |

| 6  | 6.1.  | Introducción                                    | 89  |

| 6  | 6.2.  | Instalación del entorno de desarrollo de Xilinx | 89  |

| 6  | 6.3.  | Dispositivo y tarjeta de evaluación             | 90  |

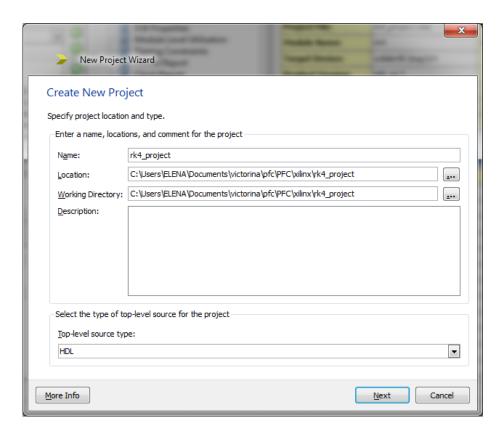

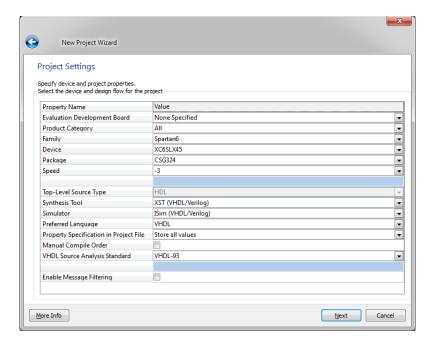

| 6  | 6.4.  | Construcción de un proyecto                     | 91  |

| 6  | 6.5.  | Fuentes VHDL                                    | 92  |

| 6  | 6.6.  | Definición de restricciones                     | 94  |

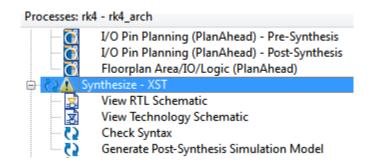

| 6  | 6.7.  | Síntesis                                        | 95  |

| 6  | 8.8.  | Implementación                                  | 96  |

| 6  | 6.9.  | Configuración de la FPGA                        | 98  |

|    | 6.9   | 9.1. Programación en modo JTAG                  | 98  |

|    | 6.9   | 9.2. Configuración en modo ROM                  | 99  |

| 6  | S.10. | Conclusiones                                    | 00  |

| 7. | DISI  | EÑO DE LA INTERFAZ DE USUARIO1                  | 01  |

| 7  | 7.1.  | Introducción                                    | 01  |

| 7  | 7.2.  | Uso de la aplicación1                           | 02  |

|    | 7:    | 2.1. Instalación                                | 102 |

|    | 7.   | 2.2. Definición gráfica del modelo                          | 102 |

|----|------|-------------------------------------------------------------|-----|

|    | 7.   | 2.3. Inicio de la aplicación                                | 104 |

|    | 7.   | 2.4. Carga del circuito                                     | 104 |

|    | 7.   | 2.5. Obtención de las ecuaciones de estado                  | 105 |

|    | 7.   | 2.6. Configuración de la simulación                         | 110 |

|    | 7.   | 2.7. Conexión del PC con la FPGA                            | 111 |

|    | 7.   | 2.8. Lanzamiento y representación de la simulación          | 113 |

|    | 7.3. | Diseño y codificación de la aplicación                      | 114 |

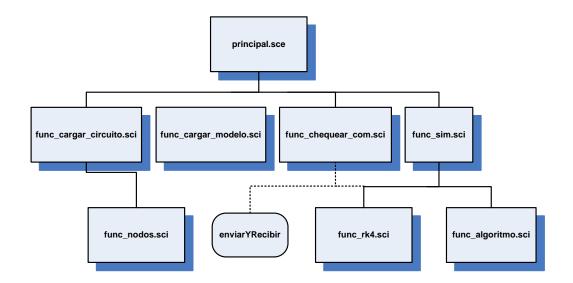

|    | 7.   | 3.1. Función principal                                      | 115 |

|    | 7.   | 3.2. Función para cargar el circuito                        | 117 |

|    | 7.   | 3.3. Función de chequeo de comunicación                     | 121 |

|    | 7.   | 3.4. Función para cargar el modelo                          | 121 |

|    | 7.   | 3.5. Función para procesar las simulaciones                 | 121 |

|    | 7.   | 3.6. Función embebida para intercambio de datos con la FPGA | 124 |

|    | 7.4. | Verificación de la construcción del modelo                  | 125 |

|    | 7.5. | Conclusiones                                                | 126 |

| 8. | VEF  | RIFICACIÓN Y VALIDACIÓN                                     | 127 |

|    | 8.1. | Introducción                                                | 127 |

|    | 8.2. | Verificación del algoritmo                                  | 127 |

|    | 8.   | 2.1. Procedimiento                                          | 127 |

|    | 8.   | 2.2. Chequeo                                                | 134 |

|    | 8.3. | Verificación del controlador Ethernet                       | 135 |

|    | 8.   | 3.1. Procedimiento                                          | 135 |

|    | 8.   | 3.2. Chequeo                                                | 138 |

|    | 8.4. | Validación del sistema                                      | 139 |

|    | 8.   | 4.1. Procedimiento                                          | 140 |

|    | 8.   | 4.2. Chequeo                                                | 140 |

|    | 8.5. | Conclusiones                                                | 140 |

| 9. | . AN | ÁLISIS DE RESULTADOS                                        | 143 |

| 9.1.           | Introducción                                                | . 143 |

|----------------|-------------------------------------------------------------|-------|

| 9.2.           | Crecimiento de la complejidad y del coste de la metodología | . 143 |

| 9.3.           | Tiempos de procesado de simulación                          | . 144 |

| 9.4.           | Conclusiones                                                | . 148 |

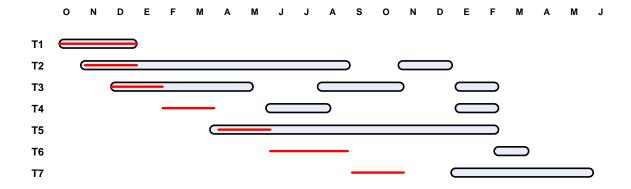

| 10.PL <i>A</i> | NIFICACIÓN Y COSTES DEL PROYECTO                            | . 149 |

| 10.1           | Introducción                                                | . 149 |

| 10.2           | Planificación                                               | . 149 |

| 10.3           | Costes del proyecto                                         | . 152 |

| 10.4           | Conclusiones                                                | . 152 |

| 11.COI         | NCLUSIONES Y TRABAJOS FUTUROS                               | . 153 |

| 11.1.          | Introducción                                                | . 153 |

| 11.2           | Conclusiones                                                | . 153 |

| 11.3           | Trabajos futuros                                            | . 154 |

| BIBLIC         | OGRAFÍA Y REFERENCIAS                                       | . 157 |

| SIGI A         | S ARREVIATURAS Y ACRÓNIMOS                                  | 161   |

## INDICE DE FIGURAS

| Figura 1.1. Estructura básica de una FPGA                                               | 22 |

|-----------------------------------------------------------------------------------------|----|

| Figura 1.2. Estructura de carpetas del proyecto en el CD                                | 27 |

| Figura 2.1. Procesos de la metodología basada en VHDL                                   | 30 |

| Figura 3.1. Funcionalidad general del sistema                                           | 33 |

| Figura 3.2. Campo de datos de un datagrama UDP                                          | 41 |

| Figura 4.1. Arquitectura del sistema                                                    | 45 |

| Figura 4.2. Campos de trama Ethernet                                                    | 46 |

| Figura 4.3. Controlador Ethernet                                                        | 47 |

| Figura 4.4. Generación del campo CRC                                                    | 48 |

| Figura 4.5. Descripción de las operaciones del algoritmo                                | 50 |

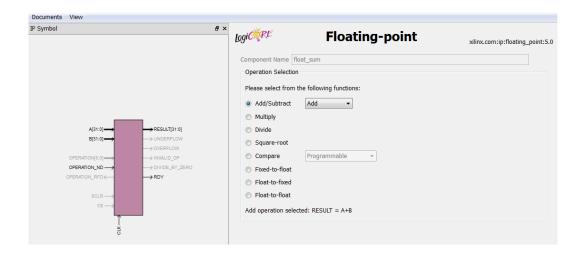

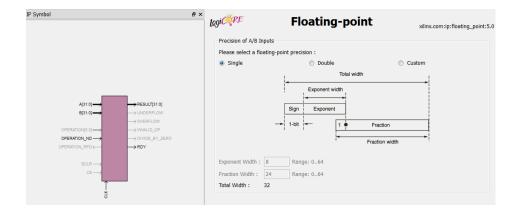

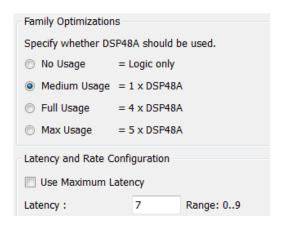

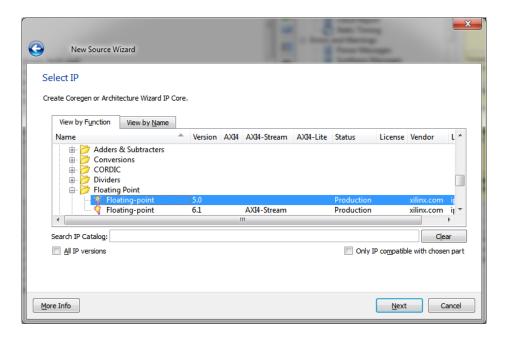

| Figura 5.1. Ventana de configuración del logiCORE Floating-point Operator               | 80 |

| Figura 5.2. Definición de la precisión del logiCORE Floating-point Operator             | 80 |

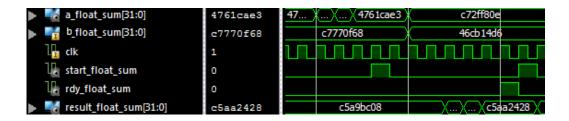

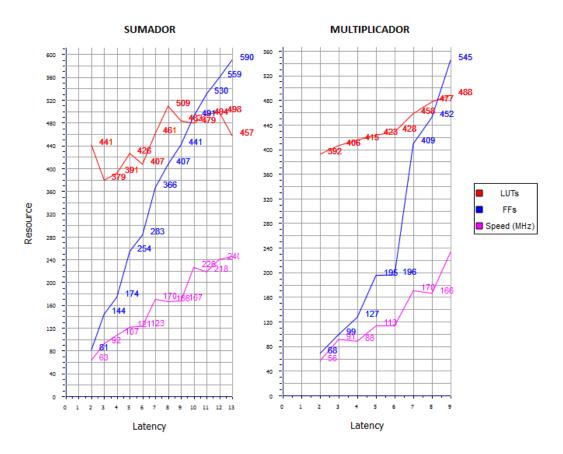

| Figura 5.3. Simulación de un sumador con latencia 7                                     | 81 |

| Figura 5.4. Configuración de la latencia del sumador logiCORE Floating-point            | 81 |

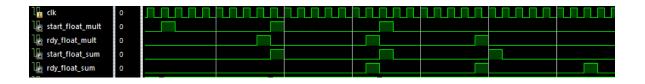

| Figura 5.5. Control de la latencia de los logiCORE Floating-point Operators en pipeline | 82 |

| Figura 5.6. Recursos empleados del multiplicador logiCORE Floating-point                | 82 |

| Figura 5.7. Estimación de los recursos en el logiCORE Floating-point Operator           | 83 |

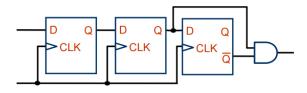

| Figura 5.8. Sincronizador de un pulso asíncrono                                         | 86 |

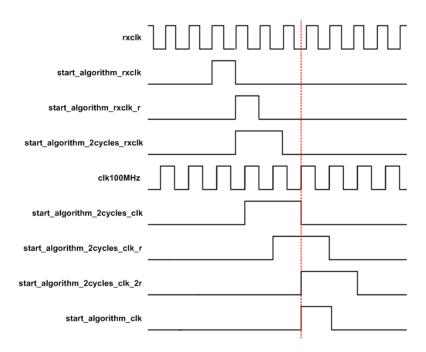

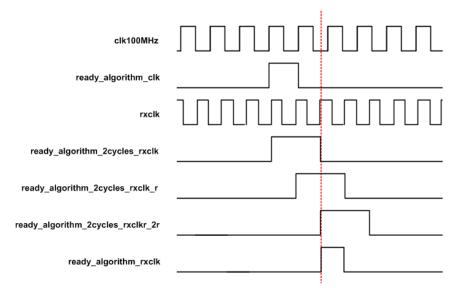

| Figura 5.9. Cambio de dominio de reloj de la señal start_algorithm                      | 86 |

| Figura 5.10. Cambio de dominio de reloj de la señal ready_algorithm                     | 87 |

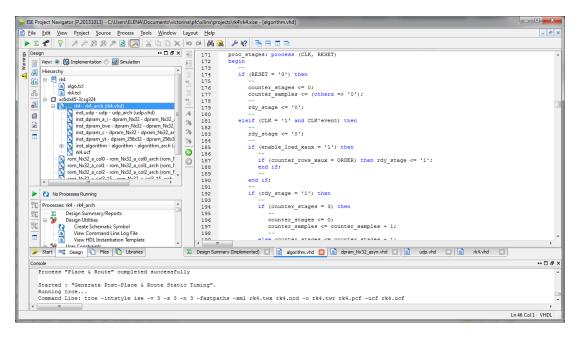

| Figura 6.1. Entorno de desarrollo de Xilinx                                             | 89 |

| Figura 6.2. Tarjeta Atlys de Digilent                                                   | 90 |

| Figura 6.3. Creación del proyecto                                                       | 91 |

| Figura 6.4. Propiedades del proyecto                                                    | 92 |

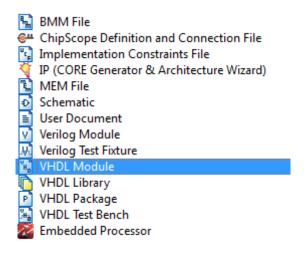

| Figura 6.5. Ventana de creación de fuentes                                              | 92 |

| Figura 6.6. Selección de cores                                                          | 93 |

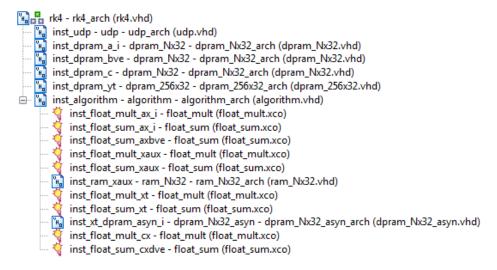

| Figura 6.7. Jerarquía de componentes                                                  | 93  |

|---------------------------------------------------------------------------------------|-----|

| Figura 6.8. Librerías                                                                 | 94  |

| Figura 6.9. Ventana de procesos para la ejecución de la síntesis                      | 96  |

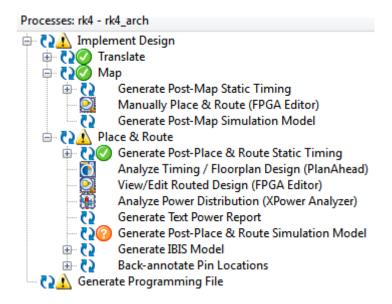

| Figura 6.10. Procesos para la implementación                                          | 97  |

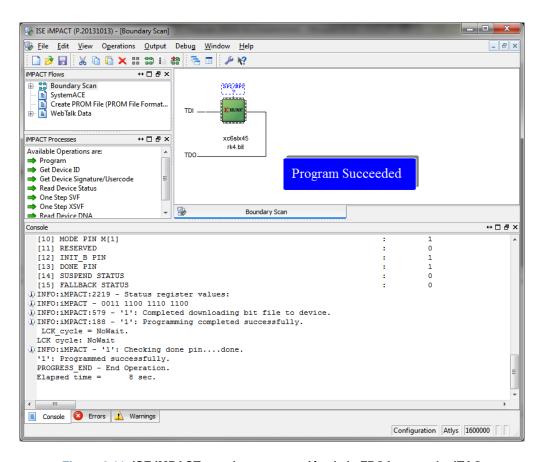

| Figura 6.11. ISE iMPACT para la programación de la FPGA en modo JTAG                  | 98  |

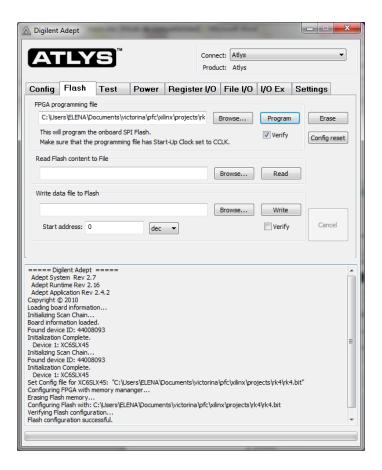

| Figura 6.12. Software Adept para la programación de la FPGA en modo ROM               | 99  |

| Figura 7.1. Interfaz de usuario para la simulación de los circuitos                   | 101 |

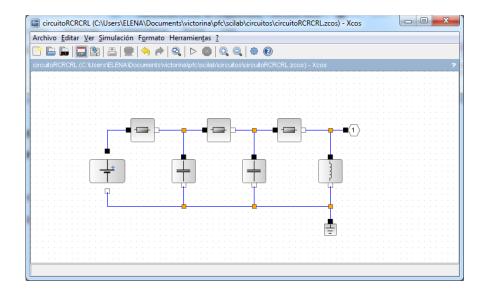

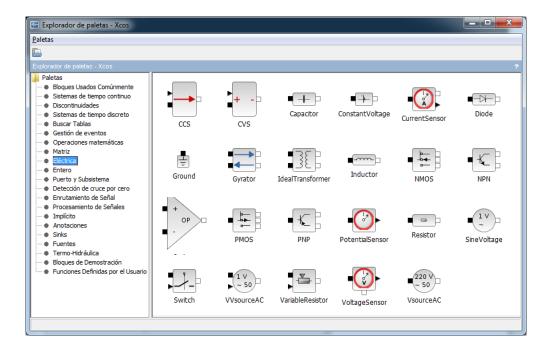

| Figura 7.2. Trazado de un circuito con Xcos                                           | 103 |

| Figura 7.3. Explorador de paletas de Xcos                                             | 103 |

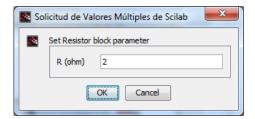

| Figura 7.4. Ventana de configuración de una resistencia con Xcos                      | 104 |

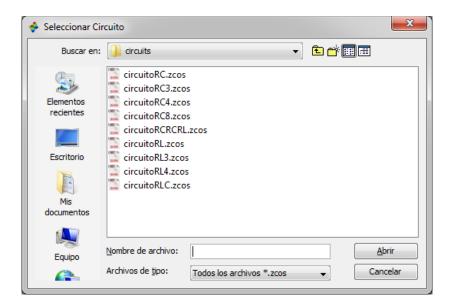

| Figura 7.5. Ventana de selección de un circuito                                       | 105 |

| Figura 7.6. Nombre del circuito en la barra de estado                                 | 105 |

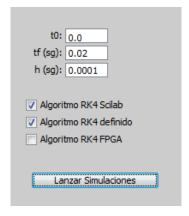

| Figura 7.7. Configuración y activación de las simulaciones                            | 110 |

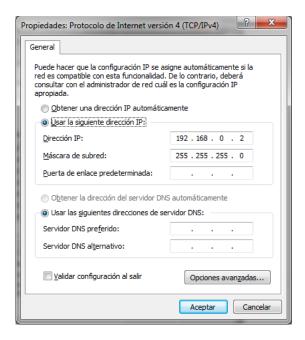

| Figura 7.8. Ventana de configuración de la conexión de área local                     | 112 |

| Figura 7.9. Ventana de estado de conexión de área local                               | 113 |

| Figura 7.10. Chequeo de la comunicación con la FPGA                                   | 113 |

| Figura 7.11. Representación gráfica de las simulaciones seleccionadas                 | 114 |

| Figura 7.12. Estructura de ficheros de la aplicación Simulaciones RK4                 | 114 |

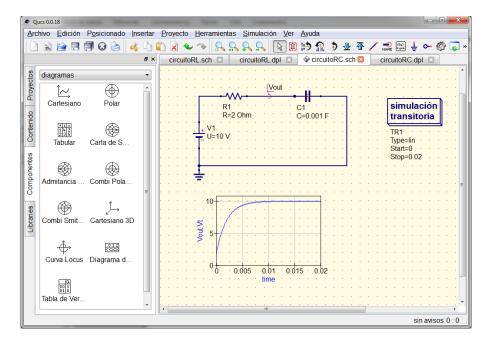

| Figura 7.13. Simulación de circuitos con Qucs                                         | 126 |

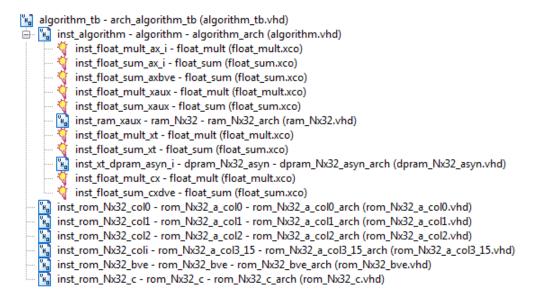

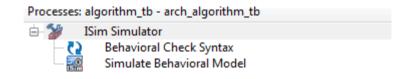

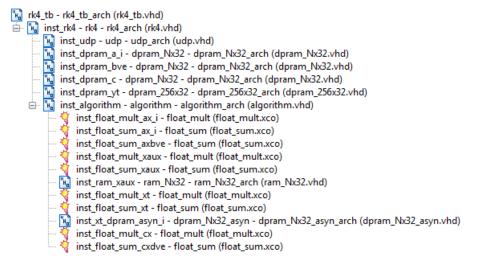

| Figura 8.1. Jerarquía de ficheros para el testbench algorithm_tb                      | 128 |

| Figura 8.2. Circuito RL de orden 3                                                    | 129 |

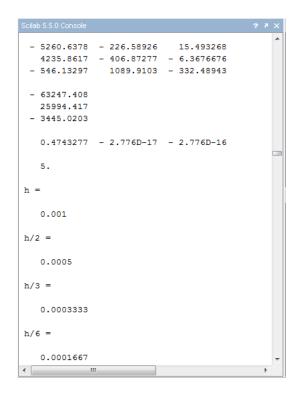

| Figura 8.3. Valores de configuración extraídos por consola                            | 130 |

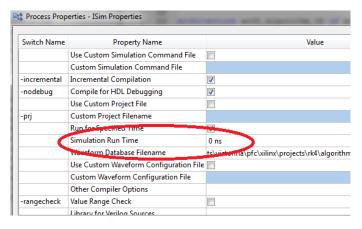

| Figura 8.4. Ventana de procesos para el testbench                                     | 130 |

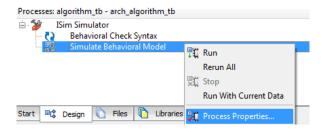

| Figura 8.5. Propiedades de la simulación                                              | 131 |

| Figura 8.6. Propiedades de la simulación                                              | 131 |

| Figura 8.7. Carga del script desde la consola de ISim                                 | 131 |

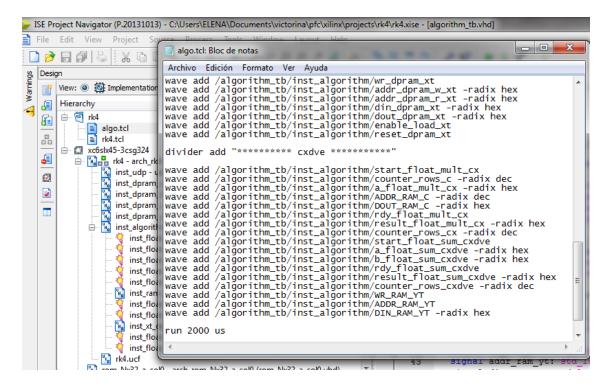

| Figura 8.8. Fichero del script algo.tcl                                               | 132 |

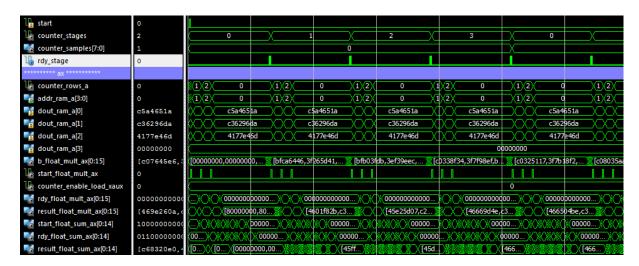

| Figura 8.9. Ventana del simulador ISim                                                | 132 |

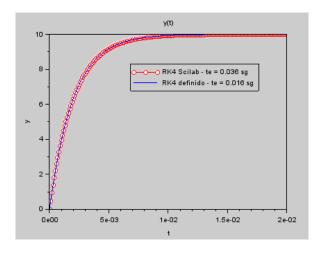

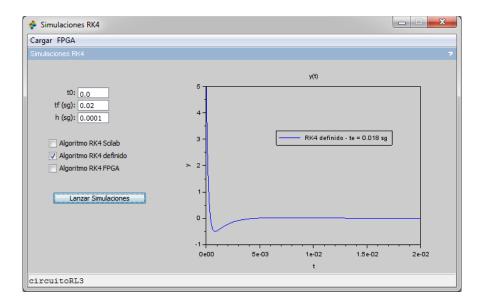

| Figura 8.10. Simulación del circuito RL de orden 3 con RK4 definido con código Scilab | 134 |

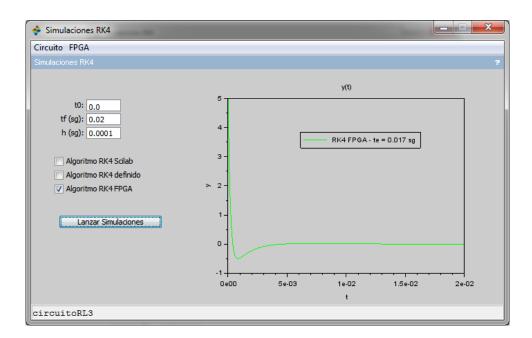

| Figura 8.11. Simulación tipo Algoritmo RK4 FPGA                         | 135 |

|-------------------------------------------------------------------------|-----|

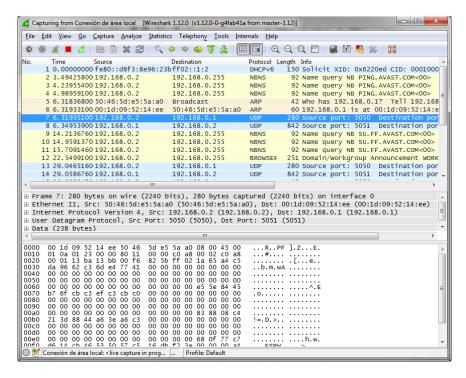

| Figura 8.12. Ventana del analizador de paquetes Ethernet Wireshark      | 136 |

| Figura 8.13. Jerarquía de ficheros para el testbench rk4_tb             | 136 |

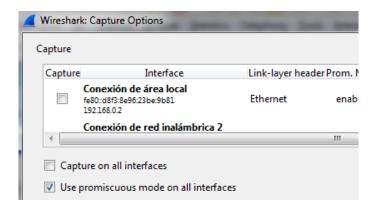

| Figura 8.14. Opciones de captura con Wireshark                          | 138 |

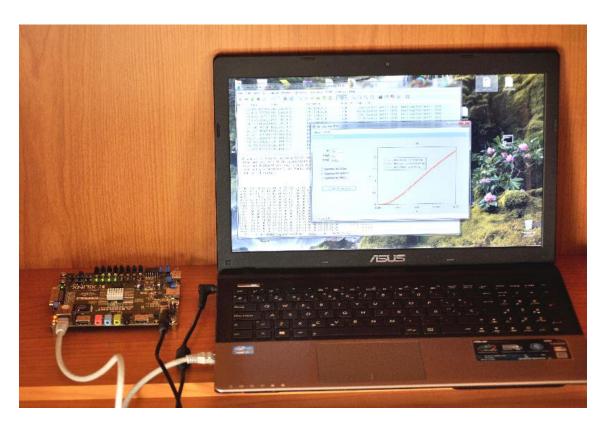

| Figura 8.15. Integración del sistema final                              | 139 |

| Figura 8.16. Comparación de las simulaciones del circuito RL de orden 3 | 140 |

| Figura 10.1. Diagrama de Gantt de progreso de tareas                    | 151 |

Sistema basado en FPGA para la simulación dinámica de circuitos eléctricos lineales

## **INDICE DE TABLAS**

| bla 4.1. Sumador que obtiene <i>res1</i> en función del orden           | 52  |

|-------------------------------------------------------------------------|-----|

| Tabla 4.2. Salida de multiplexor en función de la etapa para res2       | 52  |

| Tabla 4.3. Salida de multiplexor en función de la etapa para res3       | 53  |

| Tabla 5.1. Características de las memorias empleadas en la arquitectura | 75  |

| Tabla 6.1. Características de la FPGA adquirida                         | 90  |

| Tabla 6.2. Recursos empleados                                           | 97  |

| Tabla 7.1. Configuración de la red                                      | 112 |

| Tabla 8.1. Comportamiento de los leds                                   | 138 |

| Tabla 9.1. Tiempos de procesado de las simulaciones                     | 145 |

| Tabla 9.2. Tiempos de procesado del algoritmo con FPGA                  | 146 |

Sistema basado en FPGA para la simulación dinámica de circuitos eléctricos lineales

## 1. INTRODUCCIÓN, OBJETIVOS Y ESTRUCTURA

#### 1.1. Introducción

Antes de trazar los objetivos de este proyecto y presentar su estructura se explican de forma resumida los conceptos con los que se va a trabajar y se expone la justificación de la elección del tema abordado.

#### Modelado y simulación de sistemas

El comportamiento de un sistema físico se puede aproximar por medio de un modelo matemático compuesto por un conjunto de entradas, salidas y variables de estado relacionadas por ecuaciones diferenciales lineales de primer orden (Wikipedia, 2015). Una forma de obtener este modelo en el caso de circuitos eléctricos tipo RLC es empleando el Análisis Nodal Modificado que parte de las leyes de Kirchhoff (Hanke, 2006).

Para obtener una simulación dinámica a partir del modelo matemático del sistema se requiere la ejecución de un algoritmo que genere la respuesta transitoria. El algoritmo Runge-Kutta de cuarto orden obtiene resultados muy próximos al comportamiento real del sistema pero exige la realización de una cantidad elevada de operaciones (Nizzo, 2009).

#### Scilab

Scilab es una herramienta para cálculo numérico y simulación sobre PC de uso libre, con la que se pueden modelar sistemas físicos, ejecutar de forma eficiente código matemático desarrollado con un lenguaje de alto nivel y representar resultados numéricos en gráficas fácilmente configurables. Además incluye herramientas como Xcos que permite la edición gráfica de circuitos y las librerías JIMS con las que se puede embeber código Java en el propio

código Scilab. La herramienta también dispone de funciones para la creación de interfaces gráficas de usuario.

#### Lógica programable y FPGAs

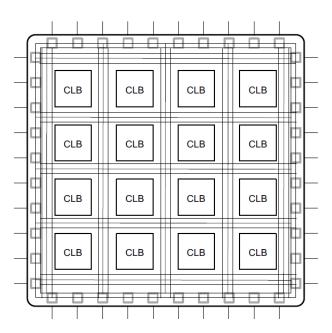

Una FPGA es un dispositivo formado por un gran número de pequeños bloques lógicos configurables (CLBs o Configurable Logic Blocks) interconectados entre sí y capaces de reproducir operaciones lógicas y aritméticas de una forma optimizada (Xilinx, 2015b).

Figura 1.1. Estructura básica de una FPGA

En la estructura de la FPGA destacan los siguientes elementos (Xilinx, 2014):

- Look-up Tables (LUTs): bloques que ejecutan operaciones lógicas.

- Flip-flops (FFs): elementos que registran el resultado de las operaciones realizadas por las LUTs.

- Hilos o buses que conectan los distintos elementos.

- Pads de entrada, salida o ambos (I/O) que son los puertos que intercambian información con el exterior.

- Bloques DSP o unidades aritmético-lógicas embebidas.

- Bloques de memoria.

Esta arquitectura de la lógica programable hace posible el paralelizado de operaciones empleando frecuencias superiores a 100 MHz por lo que favorece el desarrollo de algoritmos que requieren la ejecución de muchas operaciones en un tiempo limitado.

#### **VHDL**

VHDL (Very High Speed Integrated Circuit Hardware Description Language) es un lenguaje estandarizado por el IEEE (*Institute of Electrical and Electronics Engineers*) en la norma ANSI/IEEE 1076-1993 y que permite describir el comportamiento de un circuito digital (Floyd, 2006: 250).

Una de los formas que tiene VHDL de describir un circuito es siguiendo la Lógica de Transferencia de Registros (RTL o Register-Transfer Logic). Considerando que un circuito digital síncrono consiste en registros implementados con flip-flops (FFs) y lógica combinacional formada por puertas lógicas, una descripción RTL significa que en cada paso el circuito debe realizar una transferencia de datos entre registros y evaluar un conjunto de condiciones expresada con la lógica combinacional para pasar al siguiente paso. La descripción RTL es comprendida por los sintetizadores de VHDL que la convierten en otra descripción a nivel de puertas lógicas (Terés, 1998:182-184).

En la sintaxis de VHDL destacan elementos (Floyd, 2006: 250) como la entidad, que describe los puertos de entrada y salida del circuito lógico, la arquitectura, que describe la operación interna del circuito, el componente, una forma de predefinir un circuito que puede instanciarse repetidas veces, y la señal, la forma de especificar una conexión entre componentes (Floyd, 2006: 296). Dentro del cuerpo de la arquitectura se definen sentencias concurrentes y dentro del cuerpo de los procesos sentencias secuenciales (Wikilibros, 2015).

#### Metodología basada en VHDL

Fabricantes como Xilinx distribuyen distintas familias de FPGAs y ofrecen potentes herramientas de diseño que facilitan las tareas de descripción hardware, síntesis, verificación, implementación y configuración.

Para el desarrollo de un sistema sobre FPGA se establece una metodología basada en VHDL en la que son esenciales la especificación de requisitos, los diseños conceptual y detallado, la realización física, la verificación con generación de estímulos y la validación (Terés, 1998: 355-359).

Es interesante el uso de Intellectual Properties (IP) o cores, bloques ya construidos con una funcionalidad perfectamente definida, proporcionados por los fabricantes de FPGAs y configurables con las herramientas de diseño. Estos cores permiten al desarrollador centrarse en el propio diseño ganando en tiempo y eficiencia (Xilinx, 2015a).

#### Elección del tema del proyecto

El tema abordado en este proyecto surge del interés personal y profesional por el empleo de lógica programable para el diseño de sistemas digitales. También se pretende trabajar en un desarrollo que requiera un cierto grado de análisis matemático y que se relacione con herramientas de simulación PC y diseño de interfaces de usuario orientado a objetos. La concreción del tema parte del trabajo descrito en el artículo (Chen, 2009). Aunque este trabajo es similar al propuesto en este proyecto existen ciertas diferencias destacadas a continuación.

- El tipo de sistema físico a modelar y simular es distinto.

- Se emplean otros métodos y herramientas de validación (Matlab/Simulink vs Scilab/Xcos).

- Cambia la forma de extraer los datos de la simulación de la FPGA hacia el PC.

En este proyecto se añade la posibilidad de poder cargar en la FPGA distintos modelos configurables desde una aplicación de usuario.

#### 1.2. Objetivos

Este proyecto plantea los siguientes objetivos.

- Definir el modelo matemático de un circuito eléctrico RLC con corriente continua y optar por el método numérico idóneo para calcular la respuesta transitoria de la señal de tensión en uno de sus nodos.

- Evaluar la aplicabilidad de la metodología basada en VHDL para la obtención de la simulación dinámica del modelo matemático del circuito RLC. Debe demostrarse que son factibles la descripción correcta y eficiente del algoritmo, su síntesis, implementación y el cumplimiento de los requisitos temporales y lógicos exigidos por la arquitectura de la FPGA.

Para ello se planteará una especificación de requisitos, se realizarán el diseño de la arquitectura y su descripción con VHDL, se elegirán la tecnología de lógica programable y la tarjeta de evaluación con la FPGA adecuada, se verificarán las descripciones por medio de testbenches, se implantará físicamente el sistema hardware y se validará.

Crear un entorno de usuario desde el que se pueda extraer el modelo matemático de un circuito a partir de su representación gráfica. Una vez configurada la FPGA, que exista la posibilidad de cargar el modelo en la FPGA y que los resultados de la simulación dinámica puedan ser adecuadamente transferidos al PC y representados en una interfaz gráfica.

Es necesario previamente elegir y adaptarse a una herramienta de modelado y simulación que incluya la posibilidad de diseñar interfaces gráficas de usuario y codificar a alto nivel.

También se debe definir una forma eficiente de comunicación entre el PC y la FPGA y preparar los controladores tanto en la aplicación de usuario como en la arquitectura de la FPGA para hacer posible el intercambio de información.

Comprobar la mejora de la velocidad de procesado de la simulación dinámica del modelo sobre la FPGA en comparación con otros sistemas de simulación basados en PC.

Para ello, con la herramienta de modelado, se codificará el algoritmo de simulación elegido para obtener simulaciones basadas en PC. Posteriormente se lanzarán los dos tipos de simulación, basada en PC y basada en FPGA, se calcularán los respectivos tiempos de procesado y se representarán gráficamente para el posterior análisis de la diferencia entre ambos. Se espera obtener tiempos de simulación para el sistema basado en FPGA como mínimo inferiores en un orden de magnitud.

• Evaluar el crecimiento de la complejidad y coste de la metodología a medida que aumenta la dimensión del circuito. Este objetivo implica analizar cómo influye en el desarrollo del sistema el aumento de la complejidad del sistema modelado. Se deben conocer las dimensiones a partir de las cuales el desarrollo ya no es posible debido a limitaciones, como por ejemplo, la falta de disponibilidad de elementos lógicos en la FPGA.

#### 1.3. Estructura

#### Memoria

Una vez entendidos los conceptos a emplear y trazados los objetivos, en el siguiente capítulo se van a describir las herramientas usadas y la metodología a seguir. Posteriormente a lo largo de varios capítulos se explican las diferentes etapas del desarrollo del sistema: especificación de requisitos, diseños conceptual y detallado, realización física, verificación y validación. Se intercala un capítulo para explicar la funcionalidad y diseño de la interfaz de usuario. Se

continúa con el análisis de resultados, con la planificación y costes del proyecto y con las conclusiones y trabajos futuros. Se finaliza con un apartado de bibliografía y referencias y otro para siglas y abreviaturas.

#### CD

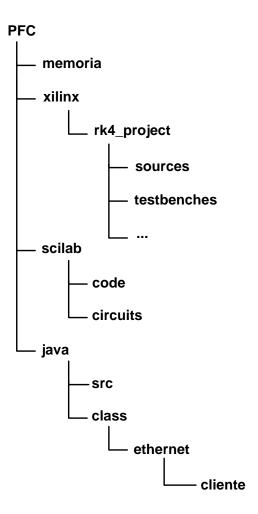

En el CD adjunto a esta memoria se proporciona la documentación, el código y ficheros generados en el desarrollo del sistema así cómo los esquemas de los circuitos empleados para el testeo, todos ellos ordenados en la estructura de carpetas de la Figura 1.2.

Figura 1.2. Estructura de carpetas del proyecto en el CD

Sistema basado en FPGA para la simulación dinámica de circuitos eléctricos lineales

En la carpeta *memoria* aparece este documento en formato pdf.

En la carpeta *xilinx* se encuentra el proyecto *rk4\_project* generado con la herramienta ISE de Xilinx y que contiene todos los ficheros (fuentes con las descripciones VHDL, testbenches, constraints, scripts, binarios, etc.) creados a lo largo de los procesos de síntesis, testeado e implementación.

En la carpeta *scilab* se encuentra la subcarpeta *code* con el conjunto de ficheros .sce y .sci que permiten lanzar y ejecutar la aplicación de usuario en Scilab. La subcarpeta *circuits* almacena ficheros .zcos con la representación gráfica de diferentes circuitos RLC.

En la carpeta *java* está salvado el código Java y el código intermedio .class para embeber el control de envío y recepción de tramas Ethernet en Scilab.

### 2. METODOLOGÍA Y HERRAMIENTAS

#### 2.1. Introducción

Una vez trazados los objetivos es fundamental establecer qué metodología se va a seguir para el desarrollo del sistema y qué herramientas se requieren. En los siguientes apartados se tratan estos puntos.

#### 2.2. Metodología

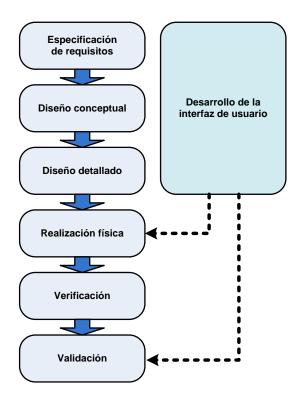

Para el desarrollo del simulador de circuitos RLC sobre una FPGA se sigue una metodología basada en VHDL en el que se llevan a cabo los procesos de especificación de requisitos, diseño conceptual, diseño detallado, realización física, verificación y validación (Terés, 1998: 355-394).

En esta metodología el diseño es tipo "top-down" (Terés, 1998: 351) lo que significa que el sistema que se desea desarrollar se va subdividiendo en módulos más sencillos con funcionalidad independiente. Estos módulos forman una jerarquía constituida por diferentes niveles siendo los niveles inferiores especializaciones del nivel superior. Esta forma de diseñar lleva a que la descripción del hardware y su verificación sean más eficientes.

En la Figura 2.1 pueden verse los diferentes procesos seguidos por la metodología. Aunque el diseño detallado, la realización física y la verificación se presenten de forma secuencial, realmente son procesos que se solapan en el tiempo.

Figura 2.1. Procesos de la metodología basada en VHDL

En paralelo al diseño de la arquitectura sobre la FPGA se genera otro flujo de diseño para crear la interfaz gráfica de usuario con la que el usuario simulará sus circuitos en el sistema final pero que además agiliza los procesos de verificación, validación y análisis de resultados.

#### 2.3. Herramientas

A continuación se enumeran todas las herramientas software y hardware que posibilitan el desarrollo del sistema junto con la funcionalidad y la forma de adquisición.

Herramienta de desarrollo **ISE** (Integrated Software Environment) Design Suite 14.7 de Xilinx de libre distribución. En la metodología de diseño elegida permite editar y analizar las descripciones VHDL, sintetizar e implementar. Incluye el simulador **ISim** para lanzar simulaciones comportamentales y el software de programación **iMPACT** para configurar la FPGA en modo JTAG.

Placa de evaluación **Atlys de Digilent** con la FPGA de Xilinx XC6SLX45 y un transceptor Ethernet para el nivel físico a 1GHz. Es adquirida por compra. Desde la página web de Digilent se puede descargar de forma libre el programa **Digilent Adept** para programar la FPGA de la placa Atlys en modo ROM.

Herramienta de computación numérica, modelado y simulación **Scilab 5.5.0** de código abierto. Incluye **Xcos** que posibilita la edición de circuitos. Desde el entorno Scilab se instalan las librerías **JIMS 1.1** de forma libre que permiten el uso de código Java en programas escritos con el lenguaje de Scilab. Para poder emplear las librerías JIMS se requiere el entorno libre **JDK (Java Development Kit) 1.8.0** que incluye JRE (Java Runtime Environment) y JVM (Java Virtual Machine).

Herramienta de simulación de circuitos **Quite Universal Circuit Simulator (Qucs) 0.0.18** de código abierto. Hace posible la visualización del comportamiento de circuitos eléctricos.

Portátil PC con procesador Intel 4-Core 2.4 GHz y tarjeta de red Realtek PCI GBE. Se emplea un cable de red CAT-6 para unir el PC con la tarjeta Atlys. Son adquiridos por compra.

Analizador de paquetes Ethernet **Wireshark 1.12** para el chequeo del tráfico de información entre el PC y la FPGA. Desde la página <a href="https://www.wireshark.org/download.html">https://www.wireshark.org/download.html</a> puede descargarse de forma libre.

#### 2.4. Conclusiones

Está definida una metodología para guiar el desarrollo del sistema y se dispone de un conjunto de herramientas. En los siguientes capítulos se describen las tareas para construir el sistema. Se comienza con la especificación de requisitos a la que sigue el diseño, la realización física, la verificación y la validación.

Sistema basado en FPGA para la simulación dinámica de circuitos eléctricos lineales

# 3. ESPECIFICACIÓN DE REQUISITOS

#### 3.1. Introducción

Elegida una metodología basada en VHDL se establecen una serie de procesos a seguir para el desarrollo del sistema. El primer proceso es la especificación de requisitos que debe definir qué requerimientos cumple la arquitectura a crear, es decir, qué funciones realiza. A continuación se enumeran los requisitos que cumple la arquitectura sobre la FPGA desarrollada en este proyecto.

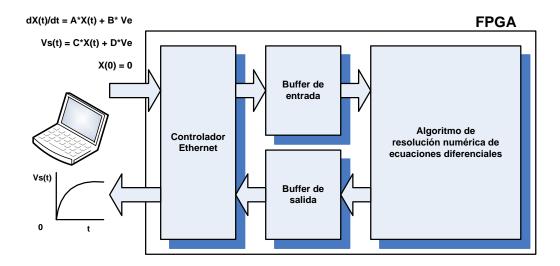

# 3.2. Funcionalidad general de la arquitectura

La arquitectura recibe como datos de entrada, a través de un controlador Ethernet, el modelo matemático que describe un sistema físico, en este caso un circuito eléctrico lineal.

Figura 3.1. Funcionalidad general del sistema

Los datos de entrada quedan almacenados y son usados por un algoritmo de resolución numérica de ecuaciones diferenciales que obtiene una solución. Esta solución, que representa la simulación del circuito eléctrico lineal, queda acumulada en un buffer y posteriormente es extraída por el controlador Ethernet hacia el PC, para su posterior representación y análisis.

# 3.3. Flujo de datos de entrada y salida de la FPGA

Los sistemas a simular son circuitos lineales que tienen las siguientes características.

- Como elemento activo se emplea una fuente de tensión V<sub>e</sub> continua (constante en el tiempo), la cual representa la única entrada del sistema.

- Los posibles elementos pasivos del circuito son:

- o resistencias con conductancia G = 1/R,

- o condensadores con capacitancia C y carga inicial nula, y además,

- o inducciones con auto-inductancia L y atravesadas por una corriente inicial nula.

- La salida del sistema o señal que se quiere simular es V<sub>s</sub>(t), también única y una de las tensiones en los nodos interiores de la malla.

Los valores de R, L y C permanecen constantes.

El modelo matemático de estos sistemas físicos (Wikipedia, 2015) viene dado por el espacio de estados:

$$\frac{dX(t)}{dt} = A \cdot X(t) + B \cdot V_e$$

$$V_s(t) = C \cdot X(t) + D \cdot V_e$$

$$X(0) = 0$$

[3.1]

donde

N es el orden del problema,

A es la matriz de estado NxN (N filas x N columnas),

B es la matriz de entrada Nx1 (N filas x 1 columna),

C es la matriz de salida 1xN (1 fila x N columnas),

D es la matriz de transmisión directa 1x1 y

X(t) es la matriz de las variables de estado Nx1. Las variables de estado representan el estado dinámico del sistema en un instante de tiempo t y forman un conjunto mínimo. Normalmente estas variables en circuitos eléctricos representan tensiones en nudos que conexionan ramas con condensadores o corrientes en ramas con inducciones.

La ecuación X(0) = 0 define las condiciones iniciales del problema, en las que, para simplificar, se consideran nulos todos los elementos de la matriz X en el instante 0.

Por lo tanto, la salida  $V_s(t)$  queda definida en función de las variables de estado representadas en la matriz X(t) y de la entrada  $V_e$ .

En la Sección 7.2.5 se desarrolla un procedimiento sistemático para obtener la representación [3.1] a partir del esquema del circuito.

De la formulación del modelo [3.1] a simular se deduce que el flujo de datos de entrada de la FPGA viene dado por los coeficientes de las matrices A, B, C y D y por V<sub>e</sub>, todos ellos constantes en el tiempo.

El flujo de datos de salida lo forman los valores reales de  $V_s(t)$  para los instantes t = 0, ..., S-1 donde S es el número de muestras de la simulación.

# 3.4. Algoritmo de resolución numérica

La arquitectura debe describir un algoritmo de resolución numérica con el que a partir del modelo matemático dado por el espacio de estados [3.1] se obtiene la solución  $V_s(t)$  para los instantes t=0, ..., S-1. De los algoritmos de resolución diferencial lineal existentes se elige el algoritmo de Runge-Kutta de orden 4 (RK4) que permite obtener  $V_s(t)$  con una aproximación muy alta con respecto a lo medido en un modelo físico real. El algoritmo se describe a continuación (Nizzo, 2009).

Dada una ecuación diferencial ordinaria de primer orden  $\frac{dX(t)}{dt} = f(t, X(t))$ , donde f es una función  $\Re \times \Re^N \to \Re^N$ , X(t) es una matriz de variables y  $X(0) = X_0$  representa las condiciones iniciales. La solución X(t) se obtiene de la siguiente forma:

Para

$$t = 0,..., S-1$$

:

$$K_1(t) = f(t, X(t))$$

$$K_2(t) = f(t + h/2, X(t) + K_1(t) \cdot h/2)$$

$$K_3(t) = f(t + h/2, X(t) + K_2(t) \cdot h/2)$$

$$K_4(t) = f(t + h, X(t) + K_3(t))$$

$$X(t + 1) = X(t) + \frac{[K_1(t) + 2 \cdot (K_2(t) + K_3(t)) + K_4(t)]}{6}$$

$$t = t + h$$

El principio de este método numérico es recoger información de cuatro puntos alrededor de la última aproximación para definir el siguiente paso.

La constante h es el paso temporal entre dos muestras y determina la precisión de la solución. Su valor también está relacionado con la estabilidad del resultado, puesto que para valores grandes de h este método numérico puede hacer que el error al hacer la aproximación crezca a medida que el cálculo avanza (Nizzo, 2009).

Si se aplica el algoritmo al espacio de estados [3.1], se tiene que f es una función independiente de f, puesto que la entrada f0 es constante:

$$f(X(t)) = A \cdot X(t) + B \cdot V_e$$

y se puede obtener la solución V<sub>s</sub>(t) de la siguiente forma:

Para

$$t = 0,...,S-1$$

:

$$K_1(t) = f(X(t))$$

$$K_2(t) = f(X(t) + K_1(t) \cdot h/2)$$

$$K_3(t) = f(X(t) + K_2(t) \cdot h/2)$$

$$K_4(t) = f(X(t) + K_3(t) \cdot h)$$

$$X(t+1) = X(t) + h \cdot \frac{[K_1(t) + 2 \cdot (K_2(t) + K_3(t)) + K_4(t)]}{6}$$

$$V_s(t) = C \cdot X(t) + D \cdot V_e$$

donde  $K_1(t)$ ,  $K_2(t)$ ,  $K_3(t)$  y  $K_4(t)$  son matrices Nx1.

A continuación se realiza un desglose del algoritmo de desarrollo propio para obtener una mejor comprensión del mismo. Previamente se definen los siguientes valores constantes de entrada:

Sistema basado en FPGA para la simulación dinámica de circuitos eléctricos lineales

$$BV_e = B \cdot V_e \quad DV_e = D \cdot V_e$$

$$H = h$$

$Hdiv2 = \frac{h}{2}$   $Hdiv3 = \frac{h}{3}$   $Hdiv6 = \frac{h}{6}$

donde BV<sub>e</sub> es una matriz Nx1 y lo demás son valores simples.

Para t = 0,..., S-1:

#### Etapa 0

Paso 0:  $res1 = A \cdot X(t)$

Paso 1:  $K = res1 + BV_e$

Paso 2:  $res2 = Hdiv2 \cdot K$

$res3 = Hdiv6 \cdot K$

Paso 3: X' = X(t) + res2

X(t+1) = X(t) + res3

### Etapa 1

Paso 0:  $res1 = A \cdot X'$

Paso 1:  $K = res1 + BV_e$

Paso 2:  $res2 = Hdiv2 \cdot K$

$res3 = Hdiv3 \cdot K$

Paso 3: X' = X(t) + res2

X(t+1) = X(t+1) + res3

#### Etapa 2

Paso 0:  $res1 = A \cdot X'$

Paso 1:  $K = res1 + BV_e$

Paso 2:  $res2 = H \cdot K$

$res3 = Hdiv3 \cdot K$

Paso 3: X' = X(t) + res2

X(t+1) = X(t+1) + res3

# Etapa 3

Paso 0:  $res1 = A \cdot X'$

Paso 1:  $K = res1 + BV_e$

Paso 2:  $res3 = Hdiv6 \cdot K$

Paso 3: X(t+1) = X(t+1) + res3

Paso 4:  $res4 = C \cdot X(t+1)$

Paso 5:  $V_s(t) = res4 + DV_e$

Donde K, X', res1, res2, res3 y res4 representan matrices con los resultados de las correspondientes operaciones.

# 3.5. Tamaño del problema

El sistema puede realizar la simulación de circuitos con un orden N en el rango de 1 a  $N_m$ , donde  $N_m$  representa el tamaño del problema y es igual a 16.

En este punto es importante aclarar que el valor del orden máximo  $N_m$  se limita a 16 para poder enviar los datos de configuración en una sola trama Ethernet y facilitar el diseño del sistema. Para un análisis más detallado ver la Sección 3.7 y la Sección 9.1.

#### 3.6. Representación de los datos

Los elementos de las matrices A, BV<sub>e</sub>, C, X(t), X(t+1), X', K, res1, res2, res3 y res4 y los valores DV<sub>e</sub>, H, Hdiv2, Hdiv3 y Hdiv6, así como el resultado de las operaciones entre ellos, son números reales y su representación viene dada por el estándar IEEE-754 con precisión simple de 32 bits. El valor del orden N se representa como un número entero tipo byte.

#### 3.7. Controlador de comunicación Ethernet

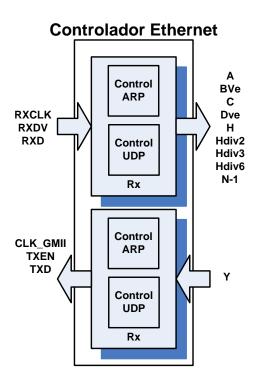

Con respecto a la capa física, la FPGA se comunica con un PC a través de Ethernet con un enlace punto a punto y recibe y transmite los datos en modo GMII a 1 Gbps. La arquitectura también gestiona las capas de enlace, de red y de transporte. De la capa de enlace existe control del protocolo ARP (Address Resolution Protocol) y a nivel de transporte el envío de datos es con UDP (User Datagram Protocol).

La FPGA recibe datagramas UDP con un campo de datos o payload de longitud fija L = 1 + 16 \* 16 \* 4 + 16 \* 4 + 4 + 4 \* 4 = 1.173 bytes con los sub-campos mostrados en la Figura 3.2. La recepción comienza con el valor N-1, donde N es el orden del sistema a simular, y acaba con el valor Hdiv6.

Con respecto a los valores de cada matriz, la FPGA comienza recibiendo la primera fila y dentro de cada fila se empieza con el elemento de la primera columna. De los elementos de las matrices A, BV<sub>e</sub> y C y de los valores DV<sub>e</sub>, H, Hdiv2, Hdiv3 y Hdiv6, se recibe primero el byte menos significativo teniendo en cuenta que están formados por cuatro bytes (32 bits en coma flotante). El valor N-1 es de un byte.

| N-1                   |

|-----------------------|

| A(0, 0)               |

| A(0, 1)               |

|                       |

| A(0, N-1)             |

|                       |

| A(N-1, 0)             |

| A(N-1, 1)             |

|                       |

| A(N-1, N-1)           |

| BV <sub>e</sub> (0)   |

| BV <sub>e</sub> (1)   |

| •••                   |

| BV <sub>e</sub> (N-1) |

| C(0)                  |

| C(1)                  |

|                       |

| C(N-1)                |

| DV <sub>e</sub>       |

| Н                     |

| Hdiv2                 |

| Hdiv3                 |

| Hdiv6                 |

Figura 3.2. Campo de datos de un datagrama UDP

La longitud del campo de datos o payload del datagrama de entrada es fijo, por lo que si el sistema a simular tiene un orden menor que 16, los valores útiles mantienen su posición y las demás celdas se rellenan con ceros.

El datagrama de salida UDP contiene los S valores del resultado de la simulación, enviando siempre del primero al último, según la representación en el tiempo de la simulación del circuito RLC, y dentro de un valor, comenzando siempre por el byte menos significativo. Para esta arquitectura se fija el valor de S a 200 muestras.

# 3.8. Almacenado de datos de entrada y salida

Los datos de entrada se almacenan en la FPGA de forma permanente durante el procesado del algoritmo. Los datos de salida se van generando y registrando en un buffer para ser enviados cuando se han completado.

### 3.9. Activación del procesado de la simulación

Una vez queda configurada la FPGA, cada vez que la arquitectura recibe un datagrama de entrada UDP se activa el algoritmo, se calcula el resultado y se transmite el datagrama de salida UDP con la solución. La FPGA debe estar preparada para recibir nuevos datagramas con las consiguientes solicitudes, incluso para simulaciones de sistemas con distinto orden.

## 3.10. Señales de reloj y reseteado

La arquitectura recibe dos relojes externos: el reloj CLK de 100 MHz para la arquitectura del algoritmo y el reloj RXCLK de 125 MHz proveniente de un transceptor Ethernet y con el que se sincronizan los datos de las tramas recibidas.

La FPGA genera un reloj CLK\_GMII para la transmisión de datos por el controlador Ethernet con el que deben estar sincronizados los datos de salida.

Se emplea un reset externo asíncrono que reinicializa todos los registros de la arquitectura.

## 3.11. Puertos de entrada y salida

En la Tabla 3.1 se definen los puertos de la arquitectura y las señales que introducen o extraen.

| Puerto    | Tipo    | Función                                              |  |  |  |

|-----------|---------|------------------------------------------------------|--|--|--|

| CLK100MHZ | Entrada | Reloj de 100 MHz                                     |  |  |  |

| RESET     | Entrada | Señal de reset asíncrono                             |  |  |  |

| CLK_GMII  | Salida  | Reloj Ethernet de salida de 125 MHz para transmisión |  |  |  |

| RXCLK     | Entrada | Reloj Ethernet de 125 MHz para recepción             |  |  |  |

| RXDV      | Entrada | Señal de validación de datos de entrada Ethernet     |  |  |  |

| RXD(7:0)  | Entrada | Datos de entrada Ethernet                            |  |  |  |

| TXEN      | Salida  | Señal de validación de datos de salida Ethernet      |  |  |  |

| TXD(7:0)  | Salida  | Datos de salida Ethernet                             |  |  |  |

Tabla 3.1. Puertos de la arquitectura

# 3.12. Conclusiones

A partir de las funcionalidades del sistema va a realizarse el diseño que mostrará cómo construir la arquitectura, conceptualmente, definiendo un conjunto de bloques interconectados, y en detalle, describiendo cada bloque con VHDL, así como el uso de cores, memorias, relojes, etc.

Sistema basado en FPGA para la simulación dinámica de circuitos eléctricos lineales

# 4. DISEÑO CONCEPTUAL

#### 4.1. Introducción

En la metodología basada en VHDL, el diseño top-down parte de un conjunto de bloques interconectados que se van de forma progresiva detallando o subdividiendo formando una jerarquía. En el diseño conceptual se define la estructura del sistema, los bloques que la forman y la conexión entre ellos. Posteriormente se hace una primera descripción de cada bloque. En las siguientes secciones se realizan estos pasos.

## 4.2. Arquitectura del sistema

En la siguiente figura puede verse el conjunto de bloques que forman la arquitectura de este proyecto sobre la FPGA, la conexión entre ellos y la interfaz hacia el exterior.

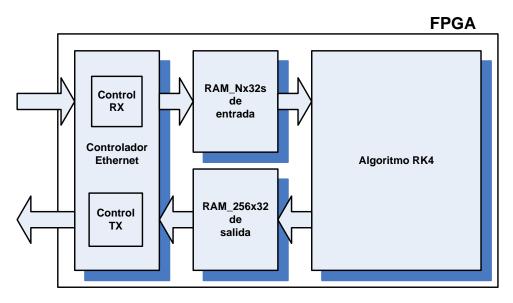

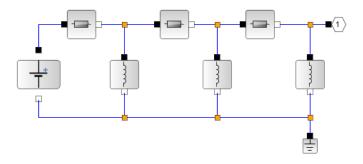

Figura 4.1. Arquitectura del sistema

El flujo de datos de la información de estado de un circuito a simular proveniente del PC es detectado y leído por un controlador Ethernet y almacenado en distintas memorias RAMs en función del tipo de información. Seguidamente se activa el procesado del algoritmo y los resultados alcanzados de la simulación del circuito se van registrando en otra memoria RAM. Cuando el algoritmo finaliza el procesado, el controlador Ethernet inicia la transmisión de los resultados hacia el PC.

#### 4.3. Controlador Ethernet

El controlador Ethernet, siguiendo la norma IEEE 802.3, selecciona, de entre todas las tramas provenientes del tráfico de red, las tramas ARP y URP enviadas por el PC hacia la FPGA.

Las tramas Ethernet (Tanenbaum, 2010: 282) están formadas por los campos mostrados en la Figura 4.2. En el campo de datos se van encapsulando las cabeceras que controlan los protocolos, como ARP (Hall, 2000: 113-114) o UDP (Hall, 2000:258-262), de los distintos niveles de la arquitectura de red.

|           | Delimitador  | Dirección | Dirección |          |                |         |

|-----------|--------------|-----------|-----------|----------|----------------|---------|

| Preámbulo | de inicio de | MAC de    | MAC de    | Longitud | Datos          | CRC     |

| 7 bytes   | trama        | destino   | origen    | 2 bytes  | 46-1.500 bytes | 4 bytes |

|           | 1 byte       | 6 bytes   | 6 bytes   |          |                |         |

Figura 4.2. Campos de trama Ethernet

El PC actúa como cliente que inicia la comunicación y la FPGA como servidor que atiende las peticiones del cliente. El controlador Ethernet recibe los bytes de las tramas de entrada sincronizados con el reloj *rxclk* y con un contador va identificando cada byte y a qué campo pertenece. El controlador también debe generar la trama respuesta para cada caso.

La primera vez que la aplicación cliente envía datos UDP se transmite previamente una trama ARP a la red para preguntar quién es el dispositivo con dirección IP (Internet Protocol) 192.168.0.1 y cuál es su dirección MAC (Media Access Control). La FPGA debe reaccionar a esta trama ARP que pide su identificación, almacenar en registros la IP y la MAC del PC cliente que inicia la comunicación y enviar otra trama ARP de respuesta con su IP y su MAC como direcciones fuente y con la IP y la MAC registradas del cliente como direcciones destino.

Cuando el controlador Ethernet recibe una trama UDP de datos, comprueba la identificación del cliente con la IP registrada anteriormente y almacena los datos útiles de entrada en las correspondientes memorias RAM y registros. Estos datos son los valores de N-1, A, BV<sub>e</sub>, C, DV<sub>e</sub>, H, Hdiv2, Hdiv3 y Hdiv6. Una vez finalizada la recepción de la trama de datos de entrada se activa un pulso de inicio de procesado del algoritmo.

Cuando la arquitectura acaba de generar los resultados activa un pulso de finalización y la FPGA envía la trama de respuesta hacia el cliente con los valores de la simulación del circuito.

Figura 4.3. Controlador Ethernet

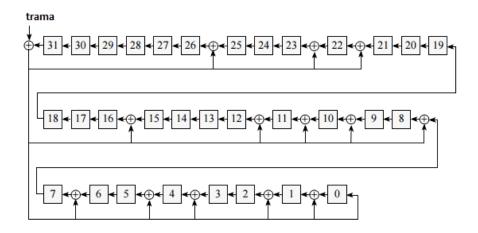

Por simplificación, el controlador Ethernet en la recepción no realiza la verificación de redundancia cíclica (CRC - Cyclic Redundancy Check) para detección de errores en la trama, pero en la transmisión es necesario añadir el campo CRC después del campo de datos para que el cliente no descarte la trama.

Consideremos que la trama a transmitir, sin los bits de preámbulo y byte delimitador de trama (Spurgeon, 2014: 52), se representa con el polinomio binario de orden k:

$$M(X) = m_k \cdot X^k + m_{k-1} \cdot X^{k-1} + ... + m_1 \cdot X^1 + m_0 \cdot X^0 \qquad \forall \ m_k = 0, 1$$

donde cada byte que forma la trama se ha colocado comenzando con el bit menos significativo.

Se tiene entonces que el campo CRC-32 (32 bits) se forma con el resto de realizar la división binaria  $X^{32+k} \cdot M(X)$  por el polinomio binario de orden 32:

$$G(X) = X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^{8} + X^{7} + X^{5} + X^{4} + X^{2} + X^{1} + X^{0}$$

A nivel lógico el campo CRC se puede conseguir con la combinación de un registro de desplazamiento y operaciones xor, como puede verse en la Figura 4.4 (Warren, 2012: 319-323).

.

Figura 4.4. Generación del campo CRC

Inicialmente los flip-flops almacenan 1s y se van cargando con el mensaje de entrada M por desplazamiento. Si el bit de entrada es 1 se aplican las operaciones xor. El valor del CRC lo forman los bits complementarios en los flip-flops después de entrar el último bit. El pseudocódigo del algoritmo completo se muestra a continuación.

#### 4.4. Memorias

Los valores de los elementos de las matrices A,  $BV_e$  y C se almacenan en memorias RAM Nx32 (N filas x 32 bits) dentro de la arquitectura de la FPGA. Las matrices  $BV_e$  y C emplean una memoria cada una, pero la matriz A requiere N memorias RAM Nx32 de tal forma que el elemento A(i, j) de la fila i y columna j, donde i, j = 0,..., N-1, se almacena en la fila i de la RAM j. Al encontrarse todos los elementos de una fila de la matriz A en memorias independientes se permite la lectura de todos ellos simultáneamente.

Las distintas muestras de la solución V<sub>s</sub>(t) se van registrando en una memoria RAM 256x32.

El algoritmo RK4 hace uso de tres memorias RAM Nx32, para los dos contextos X(t) y X(t+1) y para la matriz auxiliar X'.

Los registros de todas estas memorias almacenan palabras de 32 bits para contener valores en coma flotante siendo el bit-31 el MSB y el bit-0 el LSB.

# 4.5. Algoritmo RK4

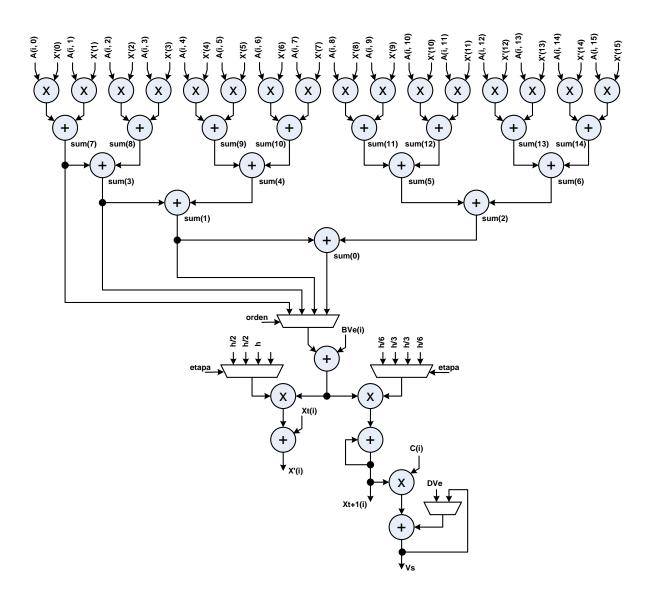

En la Figura 4.5 se describen los bloques empleados para realizar las distintas operaciones aritméticas del algoritmo. Las operaciones son sumas y productos en coma flotante sincronizadas con escrituras y lecturas en memorias RAM.

Figura 4.5. Descripción de las operaciones del algoritmo

Operaciones de diferentes pasos del algoritmo se pueden realizar simultáneamente, por lo que no es necesario finalizar todas las operaciones de un paso para iniciar otro (pipeline). Se emplean contadores para sincronizar las operaciones en cada momento y multiplexores para seleccionar el valor de ciertos operadores según la etapa.

A continuación se detallan los pasos de una etapa para el cálculo de cada muestra del algoritmo. Se denomina *ciclo de operación* al número de ciclos de reloj (100 MHz) que tarda un sumador o un multiplicador de coma flotante en realizar una operación.

#### Paso 0: si etapa = 0 entonces res1 = A \* X(t), si etapa = 1, 2 \( \tilde{0} \) 3 entonces res1 = A \* X'

Se deben obtener N valores multiplicando N elementos de cada fila de A por los N elementos de la columna de X(t-1) o X' donde N es el orden del sistema. Este producto de matrices se realiza para cada muestra t = 0,..., S-1 de la simulación durante las cuatro etapas del algoritmo, es decir 4 \* S veces, por lo que es necesario que su diseño se realice de una forma eficiente por el número de operaciones que implica.

En este diseño, para esta operación, se emplean N multiplicadores y N-1 sumadores. Al final de la etapa anterior se cargan durante N ciclos de reloj los operadores de los multiplicadores extrayendo los valores de la matriz X(t) cuando la etapa es 0 y de la matriz X' cuando son las etapas 1, 2 ó 3. En cada ciclo de operación se cargan los elementos de una fila de A en los puertos de los N multiplicadores y se multiplican por los valores de los coeficientes de X(t) o de X', que permanecen fijos en cada etapa.

Posteriormente se realizan las sumas en  $log_2N$  ciclos de operación, de tal forma que mientras se están realizando los productos para la fila 1 de A se están calculando las primeras sumas de la fila 0 y así sucesivamente. Para N = 16 la suma final se extrae del sumador 0, pero para evitar retardos innecesarios cuando el orden del sistema es menor que N, la suma final se obtiene del

correspondiente sumador en función del orden del sistema a simular. La siguiente tabla muestra el sumador que extrae el resultado final de *res1* en función del orden del sistema.

| Orden del sistema             | Sumador |

|-------------------------------|---------|

| 1, 2                          | Sum7    |

| 3, 4                          | Sum3    |

| 5, 6, 7, 8                    | Sum1    |

| 9, 10, 11, 12, 13, 14, 15, 16 | Sum0    |

Tabla 4.1. Sumador que obtiene res1 en función del orden

#### Paso 1: suma de matrices para obtener K = res1 + BV<sub>e</sub>

Para realizar esta operación de matrices Nx1 se emplea un sumador que en cada ciclo de operación va sumando al valor de una fila de *res1* el correspondiente elemento de la columna de BV<sub>e</sub>.

#### Paso 2: productos de escalar por matriz para obtener res2 y res3

En las tres primeras etapas de cada muestra, para obtener *res2* se realiza el producto de una constante por la matriz K. Para ello se emplea un multiplicador que va obteniendo en cada ciclo de operación el producto de un elemento de K por la contante. Un multiplexor determina el valor de la constante en función de la etapa, como puede verse en la siguiente tabla.

| Etapa | Salida del multiplexor |

|-------|------------------------|

| 0     | h/2                    |

| 1     | h/2                    |

| 2     | h                      |

| 3     | -                      |

Tabla 4.2. Salida de multiplexor en función de la etapa para res2

Para obtener *res3* se realiza el mismo procedimiento empleando otro multiplicador pero ahora el multiplexor extrae diferentes valores para las constantes.

| Etapa | Salida del multiplexor |

|-------|------------------------|

| 0     | h/6                    |

| 1     | h/3                    |

| 2     | h/3                    |

| 3     | h/6                    |

Tabla 4.3. Salida de multiplexor en función de la etapa para res3

#### Paso 3: suma de matrices X' = X(t) + res2 y X(t+1) = X(t+1) + res3

También simultáneamente y haciendo uso de dos sumadores, se obtienen los valores de una fila de X' y X(t+1) en cada ciclo de operación y se almacenan en una RAM Nx32. Al final de las etapas 0, 1 y 2 los elementos de la memoria X' se cargan en los multiplicadores para los cálculos de la siguiente etapa. La matriz X(t+1) parte de los valores de X(t) para la anterior muestra y va sumando res3 en las distintas etapas.

#### Paso 4: producto de matrices res4 = C \* X(t+1)

Con un multiplicador se va obteniendo en cada ciclo de operación el producto de un elemento de C por un elemento de X(t+1). El resultado pasa a un sumador que actúa de acumulador.

## Paso 5: $V_s(t) = res4 + DV_e$

Al final de la realización de todos los productos se acaba sumando al resultado de la acumulación el valor  $DV_e$ . Posteriormente se almacena este valor final en la memoria RAM de  $V_s(t)$ .

#### Inicio de cálculo para la nueva muestra

Al final de la etapa 3 en las dos matrices X(t) y X(t+1) quedan almacenados los valores del actual valor de X por lo que en la siguiente etapa 0, para la nueva muestra, ya está preparada la matriz X(t) y X(t+1) contiene el valor de partida para iniciar el resto de sumas.

## 4.6. Conclusiones

Establecida la arquitectura y descritos los distintos bloques a alto nivel se pasa al siguiente nivel de diseño en el que se aumenta el detalle de cómo el sistema realiza sus funciones y se añaden las descripciones VHDL.

# 5. DISEÑO DETALLADO

#### 5.1. Introducción

Del diseño conceptual se obtiene una estructura jerárquica de bloques interconectados entre sí y una primera descripción de cada componente. Ahora en el diseño detallado se describe con VHDL cada uno de los componentes, se define la configuración de las memorias y cores a emplear y se aclaran los puntos referentes a sincronización y dominio de relojes.

# 5.2. Descripciones VHDL

A continuación se exponen las partes de VHDL que se consideran más ilustrativas para la descripción del sistema con sus correspondientes comentarios.

#### Entidad rk4

La entidad *rk4* describe los puertos para la arquitectura principal del sistema.

```

16 entity rk4 is

port( CLK100MHZ: in std_logic; RESET: in std logic:

19

20

CLK GMII: out std logic;

TXEN: out std logic;

21

TXER: out std logic;

22

TXD: out std logic vector(7 downto 0);

23

24

RXCLK: in std logic;

25

26

RXDV: in std logic;

RXER: in std_logic;

27

28

RXD: in std_logic_vector(7 downto 0);

29

MDC: out std logic;

30

31

MDIO: out std_logic;

NRST: out std logic;

32

33

34

LED: out std_logic_vector(3 downto 0));

35 end rk4;

```

#### Arquitectura rk4\_arch

La arquitectura principal del sistema *rk4\_arch* instancia el componente *udp* con el controlador Ethernet y el componente *algorithm* con la descripción del algoritmo.

Son instanciadas además en la arquitectura *rk4\_arch* las memorias RAM de doble puerto *dpram\_Nx32* y *dpram\_256x32* que almacenan los datos de las matrices A, BV<sub>e</sub>, C y V<sub>s</sub>(t), como puede observarse a continuación.

```

inst_generate_dpram_a: for i in 0 to N-1 generate

293

294

inst_dpram_a_i: dpram_Nx32 port map(

CLK W => RXCLK,

WR => wr_ram_a,

296

ADDR_W => addr_ram_a_udp,

297

298

DIN => din_ram_a(i),

299

CLK_R => CLK100MHZ,

300

301

ADDR R => addr ram a alg,

DOUT => dout_ram_a(i));

end generate;

302

303

304

inst dpram bve: dpram_Nx32 port map(

305

CLK_W => RXCLK,

306

307

WR => wr_ram_bve,

ADDR W => addr ram bve udp,

308

309

310

DIN => din_ram_bve,

CLK R => CLK100MHZ,

ADDR_R => addr_ram_bve_alg,

DOUT => dout ram bve);

311

312

313

inst_dpram_c: dpram_Nx32 port map(

CLK_W => RXCLK,

314

315

WR => wr_ram_c,

315

316

317

318

ADDR W => addr ram c udp,

DIN => din ram c,

CLK R => CLK100MHZ,

319

ADDR_R => addr_ram_c_alg,

320

DOUT => dout ram c);

321

322

323

inst_dpram_yt: dpram_256x32 port map(

CLK_W => CLK100MHZ,

324

WR => wr ram yt,

ADDR_W => addr_ram_yt_alg,

DIN => din_ram_yt,

CLK_R => RXCLK,

325

326

326

327

328

329

ADDR R => addr ram yt udp,

DOUT => dout_ram_yt);

```

#### Entidad udp

Describe los puertos del bloque de control del controlador Ethernet.

```

19 entity udp is

20

port( RESET: in std_logic;

21

CLK GMII: out std logic;

22

23

TXEN: out std_logic;

TXER: out std logic;

24

TXD: out std_logic_vector(7 downto 0);

25

26

27

RXCLK: in std_logic;

RXDV: in std_logic;

28

29

RXER: in std_logic;

RXD: in std logic vector(7 downto 0);

30

31

32

MDC: out std_logic;

33

MDIO: out std_logic;

NRST: out std_logic;

34

35

LED: out std_logic_vector(3 downto 0);

36

37

38

ORDER: out std_logic_vector(M-1 downto 0);

39

WR_RAM_A: out std_logic;

40

41

ADDR_RAM_A: out std_logic_vector(M-1 downto 0);

DIN_RAM_A: out reg_N_32_type;

42

43

44

WR_RAM_BVE: out std_logic;

45

ADDR_RAM_BVE: out std_logic_vector(M-1 downto 0);

DIN_RAM_BVE: out std_logic_vector(31 downto 0);

46

47

WR_RAM_C: out std_logic;

48

ADDR_RAM_C: out std_logic_vector(M-1 downto 0);

49

DIN_RAM_C: out std_logic_vector(31 downto 0);

50

51

DVE: out std_logic_vector(31 downto 0);

52

53

H: out std_logic_vector(31 downto 0);

54

H_DIV_2: out std_logic_vector(31 downto 0);

55

56

H_DIV_3: out std_logic_vector(31 downto 0);

57

H_DIV_6: out std_logic_vector(31 downto 0);

58

59

ADDR_RAM_YT: out std_logic_vector(7 downto 0);

DOUT RAM YT: in std logic vector(31 downto 0);

60

61

START_ALGORITHM: out std_logic;

READY ALGORITHM: in std logic);

63

64 end udp;

```

#### Arquitectura udp\_arch

En la arquitectura *udp\_arch* el proceso *proc\_rx\_udp* contiene el control de la recepción de los datos por Ethernet. En este proceso se detecta la llegada del preámbulo (7 bytes de valor x55) y del delimitador de inicio de trama (1 byte de valor xD5) de una trama y se activa el contador *counter\_rx* que controla los bytes recibidos.

```

210

if (rxdv reg = '1') then

211

if (counter rx = 0) then

212

213

if ((check_mac = '0') and (buffer_rxd = x"5555555555555555)) then

214

215

216

counter_rx <= counter_rx + 1;</pre>

check_mac <= '1';

217

218

LED(0) <= '1';

219

220

221

end if;

222

223

else

224

counter rx <= counter rx + 1;

225

```

Conociendo la posición de cada byte en la trama recibida y con el contador *counter\_rx* se registra la información útil, como las direcciones MAC e IP del PC transmisor o el tipo de trama Ethernet.

```

if (counter rx = 6) then destin_mac(5) <= rxd_reg;</pre>

227

elsif (counter_rx = 7) then destin_mac(4) <= rxd_reg;</pre>

228

elsif (counter_rx = 8) then destin_mac(3) <= rxd_reg;</pre>

229

elsif (counter_rx = 9) then destin_mac(2) <= rxd_reg;</pre>

230

231

elsif (counter_rx = 10) then destin_mac(1) <= rxd_reg;</pre>

elsif (counter_rx = 11) then destin_mac(0) <= rxd_reg;</pre>

232

233

elsif (counter rx = 12) then ether type(15 downto 8) <= rxd reg;</pre>

234

elsif (counter_rx = 13) then ether_type(7 downto 0) <= rxd_reg;</pre>

235

236

237

elsif (counter_rx = 20) then

238

239

if (ether_type = x"0806") then opcode_arp(15 downto 8) <= rxd_reg;</pre>

end if;

240

241

elsif (counter rx = 21) then

242

243

if (ether type = x"0806") then opcode arp(7 downto 0) <= rxd reg;</pre>

244

245

end if;

246

247

elsif (counter rx = 26) then

248

if (ether type = x"0800") then destin ip(3) <= rxd reg;</pre>

249

250

end if;

```

En el registro data\_type se almacena el identificador del tipo de trama de datos UDP.

```

311 elsif (counter_rx = 42) then

312 --

313 data_type <= rxd_reg;

```

En el proceso *proc\_rx\_udp* también se añade el control para cargar en las memorias RAM los valores de A, BV<sub>e</sub> y C según van llegando los bytes de la trama de datos UDP.

```

elsif ((counter_rx > 43) and (counter_rx <= 43 + 1024)) then</pre>

319

index ram := counter rx - 44;

321

if (counter_rx(1 downto 0) = 0) then DIN_RAM_A(conv_integer(index_ram(5 downto 2)))(7 downto 0) <= rxd_reg;

elsif (counter_rx(1 downto 0) = 1) then DIN_RAM_A(conv_integer(index_ram(5 downto 2)))(15 downto 8) <= rxd_reg;

elsif (counter_rx(1 downto 0) = 2) then DIN_RAM_A(conv_integer(index_ram(5 downto 2)))(23 downto 16) <= rxd_reg;

elsif (counter_rx(1 downto 0) = 3) then DIN_RAM_A(conv_integer(index_ram(5 downto 2)))(31 downto 24) <= rxd_reg;

323

325

326

327

end if;

328

if (counter rx(5 \text{ downto 0}) = 63) then

329

330

ADDR_RAM_A <= index_ram(9 downto 6);

WR_RAM_A <= '1';

331

333

334

elsif ((counter_rx > 43 + 1024) and (counter_rx <= 43 + 1024 + 64)) then

336

337

if (counter_rx(1 downto 0) = 0) then DIN_RAM_BVE(7 downto 0) <= rxd_reg;

elsif (counter_rx(1 downto 0) = 1) then DIN_RAM_BVE(15 downto 8) <= rxd_reg;

elsif (counter_rx(1 downto 0) = 2) then DIN_RAM_BVE(23 downto 16) <= rxd_reg;

elsif (counter_rx(1 downto 0) = 3) then DIN_RAM_BVE(31 downto 24) <= rxd_reg;

339

341

343

if (counter_rx(1 downto 0) = 3) then

345

index_ram := counter_rx - (44 + 1024);

ADDR_RAM_BVE <= index_ram(5 downto 2);

WR_RAM_BVE <= '1';</pre>

347

349

end if:

elsif ((counter_rx > 43 + 1024 + 64) and (counter_rx <= 43 + 1024 + 64 + 64)) then

352

353

if (counter_rx(1 downto 0) = 0) then DIN_RAM_C(7 downto 0) <= rxd_reg;</pre>

354

elsif (counter rx(1 downto 0) = 1) then DIN_RAM_C(15 downto 8) <= rxd_reg;

elsif (counter_rx(1 downto 0) = 2) then DIN_RAM_C(23 downto 16) <= rxd_reg;</pre>

355

356

elsif (counter_rx(1 downto 0) = 3) then DIN_RAM_C(31 downto 24) <= rxd reg;

357

end if;

358

359

360

if (counter_rx(1 downto 0) = 3) then

361

index_ram := counter_rx - (44 + 1024 + 64);

362

ADDR_RAM_C <= index_ram(5 downto 2);

WR_RAM_C <= '1';

363

364

365

end if;

366

```

Además se encuentra el control para cargar los valores N-1, DV<sub>e</sub>, H, H/2, H/3 y H/6.

```

elsif ((counter_rx > 43 + 1024 + 64 + 64 + 4) and (counter_rx <= 43 + 1024 + 64 + 64 + 4 + 16)) then

if (counter_rx(3 downto 0) = 0) then H(7 downto 0) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 1) then H(15 downto 8) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 2) then H(23 downto 16) <= rxd_reg;</pre>

379

381

elsif (counter_rx(3 downto 0) = 3) then H(31 downto 24) <= rxd_reg;

383

elsif (counter_rx(3 downto 0) = 4) then H_DIV_2(7 downto 0) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 5) then H_DIV_2(15 downto 8) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 6) then H_DIV_2(23 downto 16) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 7) then H_DIV_2(31 downto 24) <= rxd_reg;

384

385

386

387

388

elsif (counter_rx(3 downto 0) = 8) then H_DIV_3(7 downto 0) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 9) then H_DIV_3(15 downto 8) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 10) then H_DIV_3(23 downto 16) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 11) then H_DIV_3(31 downto 24) <= rxd_reg;

389

390

391

392

393

elsif (counter_rx(3 downto 0) = 12) then H_DIV_6(7 downto 0) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 13) then H_DIV_6(15 downto 8) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 14) then H_DIV_6(23 downto 16) <= rxd_reg;

elsif (counter_rx(3 downto 0) = 15) then H_DIV_6(31 downto 24) <= rxd_reg;</pre>

394

396

398

end if:

```

Al final de la trama recibida se determina si ésta es de tipo ARP o es un datagrama UDP. Si es una trama ARP se define la cabecera de la trama ARP de respuesta y se activa su transmisión con el pulso *start\_tx*.

```

407

if (check mac = '1') then

408

if (ether type = x"0806") then

410

if ((opcode_arp = x"0001") and (target_ip = source_ip)) then

411

412

packet arp <= '1';

413

414

LED(1) <= '1';

415

417

--// cabecera MAC para IEEE 802.3 Ethernet (14 bytes) ///

418

419

420

header_tx(0) <= destin_mac(5);

-- DA --> MAC del destino (cliente)

421

422

header_tx(1) <= destin_mac(4);

header_tx(2) <= destin_mac(3);

423

424

header_tx(3) <= destin_mac(2);

header_tx(4) <= destin_mac(1);

header_tx(5) <= destin_mac(0);</pre>

425

426

427

header_tx(6) <= source_mac(5);

-- SA --> MAC de la fuente (fpga)

428

429

header_tx(7) <= source_mac(4);

473

header_tx(38) <= destin_ip(3);

header_tx(39) <= destin_ip(2);

header_tx(40) <= destin_ip(1);

474

475

header_tx(41) <= destin_ip(0);

476

477

478

size_header_tx <= 42;

479

size data tx <= 18;

480

481

start tx <= '1';

```

Si la trama recibida es un datagrama UDP, se debe diferenciar entre tramas de tipo solicitud de reconocimiento de comunicación (data\_type = x06) y tramas de activación del algoritmo de

simulación (*data\_type* = xFF). Cuando se recibe una trama del primer tipo se activa la transmisión directamente.

```

485

elsif (ether_type = x"0800") then

486

if (target_ip = source_ip) then

487

LED(2) <= '1';

489

490

if (data_type = x"06") then

-- solicita reconocimiento de comunicación

491

492

start_tx <= '1';

493

494

elsif (data_type = x"FF") then

-- solicita activación de algoritmo

495

496

wait_tx <= '1';

497

START ALGORITHM <= '1';

498

499

500

end if;

501

packet_arp <= '0';

502

503

504

--// cabecera MAC para IEEE 802.3 Ethernet (14 bytes) ///

505

506

507

header_tx(0) <= destin_mac(5);

-- DA --> MAC del destino (cliente)

508

header_tx(1) <= destin_mac(4);

header_tx(2) <= destin_mac(3);</pre>

509

510

header_tx(3) <= destin_mac(2);

511

header_tx(4) <= destin_mac(1);

512

513

header_tx(5) <= destin_mac(0);

514

header_tx(6) <= source_mac(5);</pre>

-- SA --> MAC de la fuente (fpga)

515

header_tx(7) <= source_mac(4);

516

header_tx(8) <= source_mac(3);

header_tx(38) <= value(15 downto 8);

header_tx(39) <= value(7 downto 0);</pre>

594

595

596

header_tx(40) <= x"00";

597

598

header_tx(41) <= x"00";

599

size_header_tx <= 42;</pre>

600

size_data_tx <= data_size;

601

```